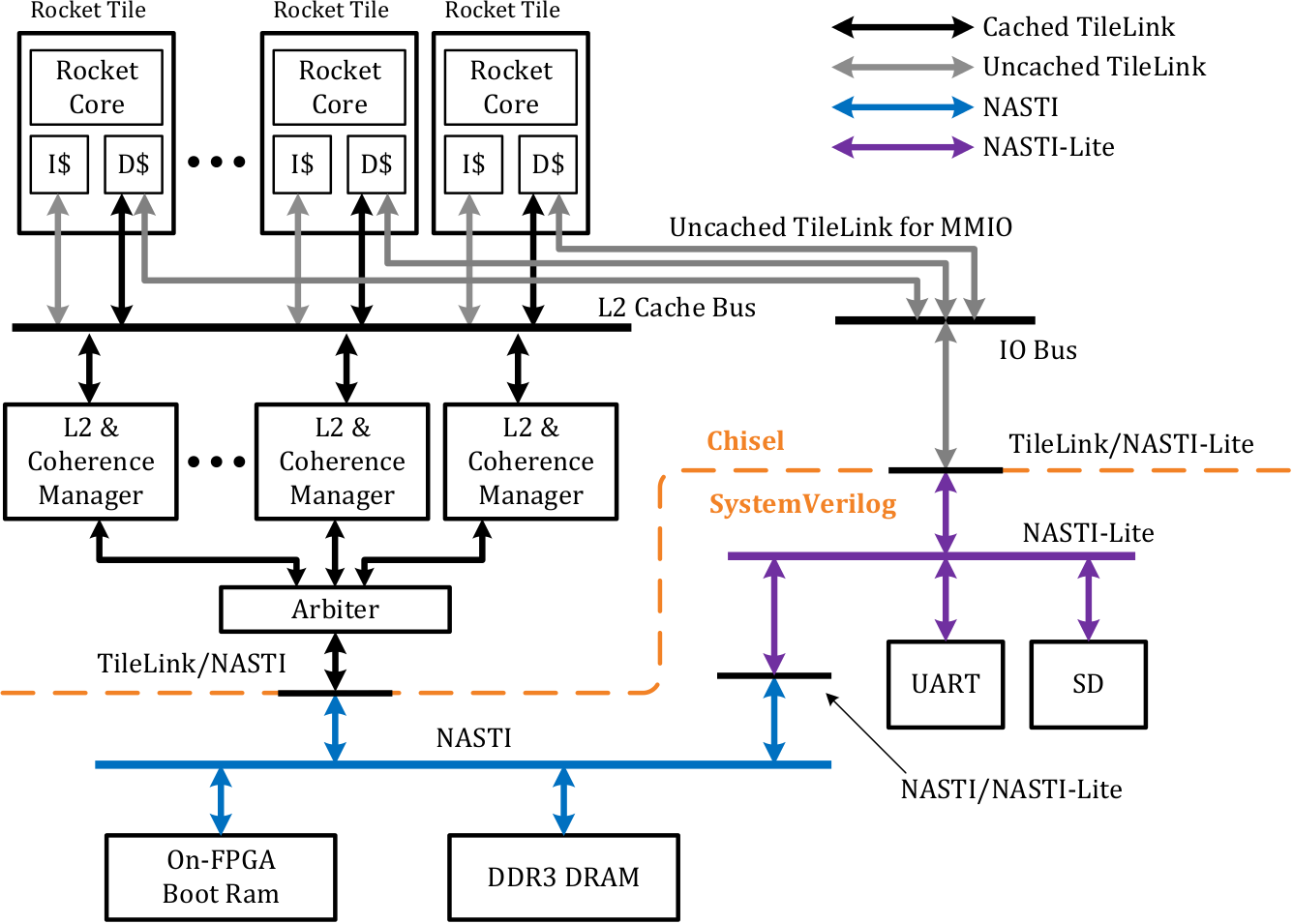

GitHub - ThalesGroup/risc-v-chisel-project: This is a starter template for your custom RISC-V project. It will allow you to leverage the Chisel HDL and RocketChip SoC generator to produce a RISC-V SoC with

プレスリリース】次世代ハードウエア記述言語入門書『Chiselで始めるデジタル回路設計』を5月31日-6月2日開催RISC-V Days参加登録者から10名様に贈呈 | 一般社団法人 RISC-V協会 | プレスリリース配信代行サービス『ドリームニュース』

![PDF] RISC5: Implementing the RISC-V ISA in gem5 | Semantic Scholar PDF] RISC5: Implementing the RISC-V ISA in gem5 | Semantic Scholar](https://d3i71xaburhd42.cloudfront.net/60726dc6963088a7ecf98c0b033bb0a3d98d16a0/5-Table4-1.png)